一款手機的充電結構如下,主要是聯發科平臺芯片,輔助是TI。

兩者可以單獨工作也可以同時工作,分開放置的目的是為了更好的散熱。

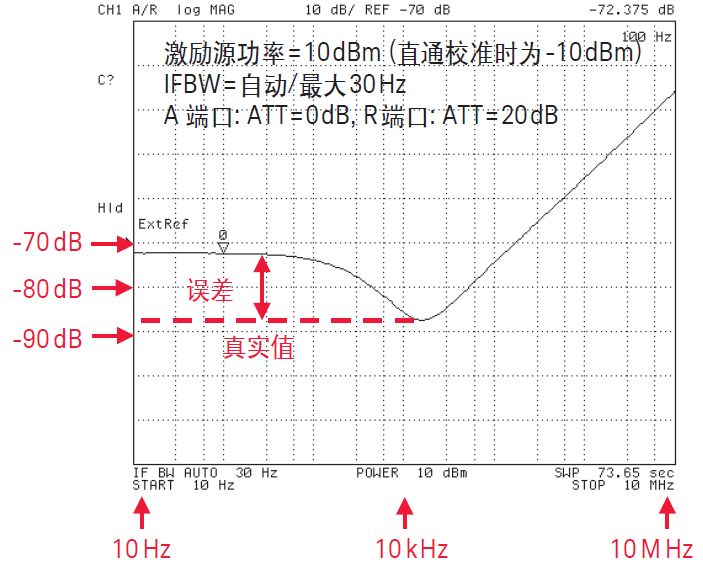

單獨工作時,當軟件設置的電壓超過1.5A時,測得進入電池的電壓總是小于設置值。 結果如下:

經過交叉驗證,這個IC換成了TI的EVB,電壓偏差在要求范圍內充電電流過大會引起,IC本身沒問題。

檢查寄存器配置,軟件反饋沒有問題。

然后專注于PCB。 下面是內部結構圖,Q4的存在證明這個充電IC是一個帶電源路徑管理的IC。

放大Q4的部分,可以看到這個IC是通過測量Q4的電壓來判斷設定電壓是否正確的,那么如何知道Q4的電壓呢?

Q4好像是由5個并聯的MOS組成,每個MOS是一個充電通道充電電流過大會引起,當充電電壓設置在1.5A以下時,通道的阻抗為8mohm,當充電電壓設置在1.5A以上時; 芯片內部只檢查5個通道中間通道的電壓是否正常。

當時的手機工程布線情況如下:

可以看出這5個通道分別占用了5對Pad。 這個路由不好。 由于走線的阻抗,最里面的MOS電流通路阻抗最小,最下面的MOS電流通路阻抗最大。 我們對走線阻抗做出以下假設:

圖中的估計并聯阻抗是從第一個通道看的估計阻抗。

根據通道3兩端的電流判斷實際電壓值與設定電壓值是否一致。 比如寄存器設置充電電壓為1.5A,那么只要測得通道3的電壓為0.3A,芯片就認為是正常的。

當通道3的電壓為0.3A時,其他通道的電壓估算如下:

從通道3的兩個焊盤來看,通道2和4的阻抗相同,通道1和5的阻抗相同。

通道2和4的電壓=0.3Ax8/10=0.24A;

通道1和5的電壓=0.3x8/12=0.2A;

所有通道電壓之和=0.3A+0.24x2+0.2Ax2=1.18A。

事實上,實際電壓并不等于設定電壓。

因此,這個問題的根本原因是PCB引起的。 VSYS和VBAT走線不好,5路MOS的電壓通路不對稱。

解決方法如下:

1、Vbat和Vsys的PIN都包了一大塊銅皮,加厚以降低阻抗。

2. 確保每個通道的阻抗是對稱的。

明天的文章到此結束,希望對大家有所幫助,下期見。