本文企圖闡明開關電源設計與測試中的若干細節問題,這是一些比較容易被忽略的小細從圖片庫選擇節。

一、紋波的檢測

(一)、紋波的組成成份

電源性能的最直觀的表現是電源雜訊,所謂電源的雜訊就是指電源輸出電流的波動。

若果是開關電源,輸出雜訊是有規律的擺動,擺動的頻度等于開關頻度。諧波的產生是由于電壓流過輸出電容在電容的ESR上所引發的壓降,開關電源中不斷地有脈動的電壓流經電容,所以它的雜訊的頻度等于開關頻度。

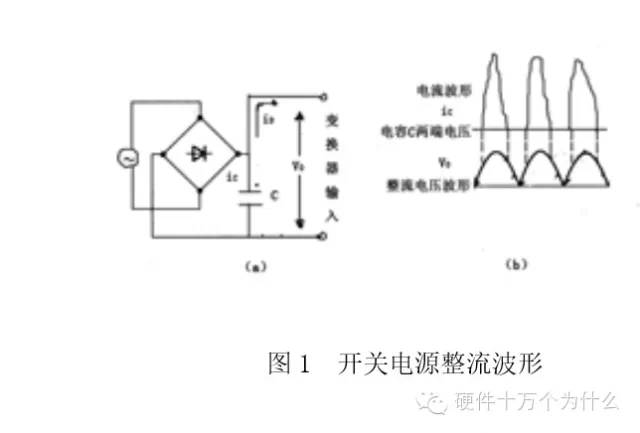

圖1、開關頻度為的開關電源的輸出雜訊

之后,悉心的你就會發覺,脈動的電流波動上疊加了細細的“針針”,這是開關電源開關訊號所引發的開關噪聲。為此,確切地說,電源的輸出波動實際上有兩個部份組成,雜訊與噪聲。

圖2、電源的輸出波動的分解

后面已提到諧波的產生是由于脈動的電壓流過輸出電容,之后在電容的ESR上所產生的壓降,所以要想剿滅雜訊是不可能的,只能是盡可能地去降低。

而疊加在雜訊上的噪聲卻是有機會得到改善的,在開關電源中,開關管造成的開關噪聲會疊加到輸出電流上,之后由于其頻度好多,很難被混頻器濾除,所以容易擴散至整個PCB板子,導致EMC問題。

關于開關噪聲的改善,下文再詳盡論述。在想辦法解決問題之前,我們須要獲得確切的信息來作決策的根據,錯誤的信息輸入必定得到愈發錯誤的決定。

(二)、如何正確地檢測電源的輸出電流的諧波?

為了表述的便捷,我們通常把輸出電流的波動也稱為雜訊,并且我們在內心深處必須時刻有一個根深蒂固的概念,我們在測試時實際上是為了獲取兩個信息:雜訊電流以及噪聲。

雜訊電流的產生與脈動電壓和電容的ESR相關,所以在測試時須要分別測試不同負載電壓下的雜訊電流,這是基于不同的脈動電壓的審視。最須要的注意的是不要人為地降低ESR,所以測試時須要在輸出電容的兩端就近檢測,否則路徑會額外降低ESR值。

噪聲的產生與開關路徑上的寄生電感相關,所以在測試時須要注意不能引進額外的寄生電感,否則測試所得的開關噪聲會小于實際值。

圖3和圖4是兩種錯誤的雜訊檢測的方式,它們正確的地方是在電容兩端就近檢測,錯誤在于引入或則說吸收了噪聲,致使測試所得的結果偏離實際情況。

圖3、錯誤的雜訊檢測方式

圖4的錯誤很容易被忽略,就是在測試時必須移除多余閑置的探棒,防止人為地引入噪聲。

圖4、在雜訊檢測時,請移除多余的閑置探棒

圖5、正確的雜訊檢測方式

正確檢測雜訊的姿態是使用雜波帽,如圖5示意,這樣可以保證檢測路徑最短,引入的噪聲最少。

圖6、簡易高效的雜訊檢測方式

假如,手頭條件有限,沒有雜訊帽咋整?雖然很簡單,可以自制。在密集檢測時,還可以使用圖6的方式,將自制的雜訊帽直接焊到PCB板上。

(三)、如何高貴地檢測電源的輸出電流的諧波?

前文講了怎樣正確地檢測雜訊,為何要如此做,這樣做的原理是哪些,等等。好多事情算是老生常談了,相信多數人是曉得的而且很熟悉的。

在這兒,我想再提一個概念,高貴地測試。后面是談怎樣正確地檢測。正確檢測是一個技術問題,有具體的操作步驟和規范,而端莊是一個心態問題,好多時侯你會發覺兩個不同的人基于同樣的儀器和操作指南卻得到了不同的檢測結果。

圖7是測試人員在測試雜訊時,探棒沒有“站直”,斜躺下,結果很不幸躺到了電感上,而電感是幅射源。在指責其檢測結果時,他還委屈,說采用了雜訊帽,并且是就近檢測的啊。后來,仔細觀察方才發覺檢測的坐姿有問題。

圖7、不同的檢測坐姿,得到不同的結果

(四)、如何評估檢測結果的正確性?

看了前文的表述,你或許會很緊張,怎么能夠保證每一個測試的坐姿都是十分之高貴呢?是否每一項測試都須要親力親為呢?

雖然是有好多小技巧去判定測試結果是否可信的,在電源的測試中,會有好多小的子項目的測試,子項目之間實際上有關聯的,悉心的你定能“火眼金睛”的看出報告里的隱情。

繼續前文圖7的測試結果,開關噪聲由于沒有被混頻器濾除有殘留,殘留被疊加到輸出電流上產生噪聲。所以,往后溯源很容易找到噪聲的源頭,而圖7的測試報告里,發覺由開關管輸入到電感的開關節點的電流訊號的過沖和下沖算是比較好的(如圖8),不可能引起這么大的輸出噪聲,這是理直氣壯地指責測試方式有問題的按照。

圖8、BUCK電路中,與電感之間的開關節點()的電流波形

假如你是一位測試人員,在測試時須要做好自檢的工作,防止后續何必要的返工,以下思路供參考。

電感是一個很強的幅射源,開關噪聲不但通過傳導也會以空間幅射的方式,往外充溢。為了防止空間中幅射的噪聲對測結果的欺騙,可有以下兩個對策來應對。

1)、在測試時,探棒可嘗試不同的坐姿,選擇一個空間幅射對測試結果影響最小的坐姿。

2)、對測試結果的交叉驗證可以降低錯誤結果發生。輸出電流上的開關噪聲,實際上和是有對應關系的。

的邊緣振鈴通常無法被輸出混頻器處理掉,最終表現為輸出電流上的開關噪聲。假如輸出電流上的開關噪聲很大,而且的邊緣振鈴卻不顯著,則說明你所測試到的噪聲很可能是來自空間中的幅射,此時可動一動探棒與PCB板子的傾角,努力將接收到的空間幅射減少到最小。

二、電源噪聲的處理

前文詳盡闡釋了雜訊的組成、紋殃及噪聲的形成機理、如何正確地檢測雜訊、如何交叉驗證測試結果確保報告的可靠性等等。測試是為了發覺問題,預警風險,包括已知的以及潛在的。若果是光測試而不解決問題等于是耍流氓。接出來,我們來談一談怎樣解決雜訊相關的問題,以BUCK電路為例。

圖9、BUCK的原理模型

開關電源的LC混頻器幾乎是沒有減少雜訊份量的能力的,由于基極是脈動電壓流過輸出電容,在電容的ESR上造成的壓降。所以,假若須要增加集電極電流,就須要增加電容的ESR,可以選用LOWESR的電容,也可以多個電容并聯來增加ESR。而且凡事都不是絕對的,假如占空比電流早已可以符合負載的需求了,就不要去追求完美了,非常是使用疊加電容的手段來減少雜訊,過大的輸出電容是有副作用的。

開關電源的LC混頻器對開關轉換時形成的邊緣噪聲更是無能為力,開關噪聲會形成更高頻的紋波,最大的弊端是對EMC性能導致負面影響。

開關噪聲與開關波形的上升/增長時間以及路徑上的寄生電感息息相關,寄生電感的改善比較麻煩,與設計相關,也和芯片的內部設計及性能相關。通常比較常采用的方式是增加開關訊號的上升與增長時間,這樣做的副作用是降低了開關過程中的交越導通耗損,在一定程度上減少了電源的效率。

所以,優化輸出紋殃及噪聲性能實際上是在找尋一個平衡點,我們須要有全局意識,切不可為了某一個單項的指標而“不折手段”。

1)、外置的開關斜率調整

圖10、外置,基極串聯內阻調整開關斜率

假如開關電源的是內置的電源電流過大電壓波動,可嘗試用一個小阻值與基極串聯,但這對開通和關斷電流均有影響,假如的關掉時間過長,則有上下管直通的風險。

因而,通常的原則是“打開慢一些,電壓變化都會緩一些,由寄生電感形成的振鈴也都會小一些;關掉的時侯利索一些,不能讓另左側的管子等待太久”。假如打開與關掉的斜率難以協調,不妨嘗試配置不同的載流子阻值,之后使用三極管進行隔離,如圖11。

圖11、外置,基極串聯內阻分別調整上升與增長斜率

2)、內置的開關斜率調整

集成度高的DC-DC變換器已將集成,所以我們難以通過基極串內阻的方法來緩解開關斜率。在這些情況電源電流過大電壓波動,若果上管是N-的話,芯片會有一個的管腳(BOOT)。可以使用一個小阻值(一般為10~20歐姆)與驅動級(BOOT)的耦合電容串聯,這在一定程度上可以緩解開關的斜率,如圖12所示。

圖12、集成,BOOT管腳串聯內阻調整開關斜率

3)、開關噪聲的吸收

在設計中建議預留緩沖電路()的位置,與下管或則續流晶閘管并聯。

設計無明晰的估算公式,由于板子的寄生參數及環境千差萬別,所以基本上是靠實際調試和逐漸迫近。以下調試的套路,僅供參考:

圖13、的調試

1、測量未接電路時的振蕩訊號周期(1/fo);

2、將高頻電容(Co)跨接在要吸收的元件上,確定電容的值,緩解振蕩使周期是原先周期的三倍;

3、確定電容以后,與電容串聯的阻值可用以下公式大概推算:

有好多R和C的組合可以形成滿意的波形,但上述R和C的選值應當形成最小的耗損和最有效的療效。同時,防止電路對開關波形的損傷。

4)、攔截開關噪聲

不管采用何種舉措,開關噪聲終究是難以回避的。為了降低系統的整體噪聲,不得不采用圍追阻截的舉措。

首先,在電源的“入口”阻擋(例如安放一粒100nF的旁路電容);

之后,在電源系統的內部盡量減小噪聲(緩解開關斜率、安裝電路、減小寄生參數等);

最后在“出口”處,盡可能做好攔截(降低LC或Bead-C混頻器)。

公眾號推薦:電源研制精英圈(已有5W+電源工程師關注)

張飛實戰電子