引腳保護。

首先是阻抗匹配。 由于信號源的阻抗很低,與信號線的阻抗不匹配,因此在內部串聯電阻可以改善匹配,從而減少反射、防止振蕩等。

其次是它可以降低信號邊緣的粗糙度,從而減少高頻噪聲和過沖。 由于串聯電阻、信號線的分布電容和負載的輸入電容形成RC電路電阻的串聯和并聯教學視頻,這將增加信號邊緣的堅固性。 要知道,如果信號的邊緣非常陡峭,并且含有大量高頻成分,就會輻射干擾,此外,還容易造成過沖。

問題1:看原理圖時,經常會聽到串聯一些小電阻值,比如22/27/33/100歐姆,但其實沒有必要。 同樣的情況,有的串起來,有的不串起來。 有哪位專家可以給我一些建議嗎?

答:如果高速信號線串接的電阻值很小,就是終端阻抗匹配。 如果將一個小電阻(/100 歐姆)連接到 GPIO 端口,它可能會抵抗小能量電流脈沖。

一個簡單的例子:并口通信的提示信號。 并口連接時,由于突然插拔,會形成很窄的電流脈沖。 如果這個脈沖直接打到GPIO口,很可能會損壞芯片,造成串連。 電阻值小很容易消耗功率。 如果脈沖是5mA5.1V,經過30ohm后就5v左右了……

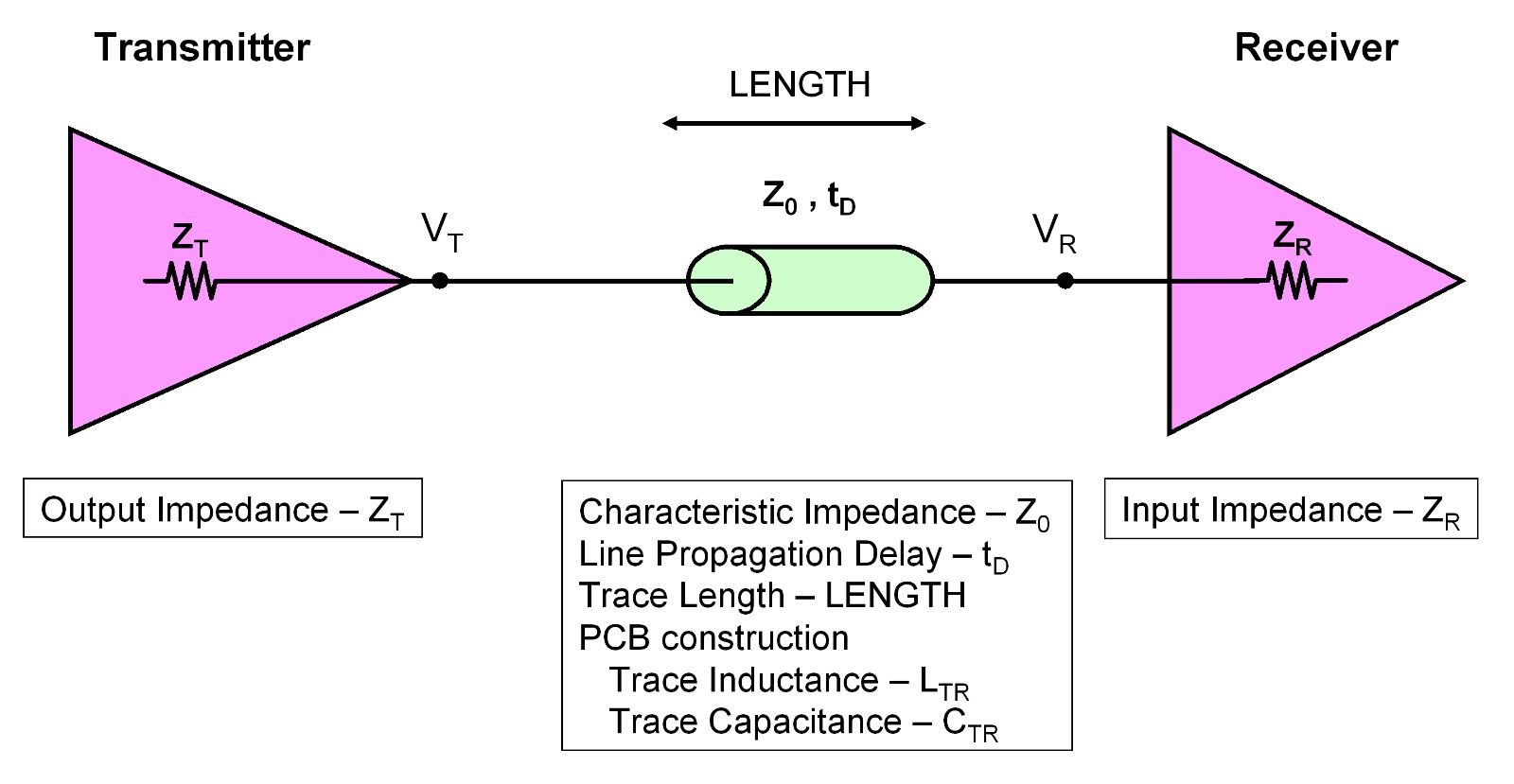

B繼續:嚴格來說,當高速電路中進行阻抗匹配,且信號在傳輸介質上的傳輸時間小于信號上升沿或增長沿的1/4時,傳輸介質就需要進行阻抗匹配。 避免電流脈沖對芯片的影響!

通常當PCB走線的寬度小于傳輸信號波長的1/10時,我們需要考慮阻抗匹配。 (我也不懂,不過據說應該是關于電磁學的,電磁學我沒學過……以后再學)

上述高速數字電路可以考慮阻抗匹配。

答案C:主要是基于阻抗匹配考慮,以達到時序統一,延遲時間、布線電容等都不會超出范圍! 原因可能是接線不匹配!

問題二:在高速信號中,我們經常會看到信號線上有小電阻串。 應該放在CPU端好還是放在信號端好? 我見過一些GPS公版方案是放在CPU端的,但我也見過其他的原理圖是放在信號端的。 請用理論來支持我!

答:通常的做法是在信號源端接一個小電阻,在信號端接一個小電阻。 在信號源端串接一個小電阻值沒有公式理論:通常傳輸線的特性阻抗約為50歐姆,TTL電路的輸出內阻約為13歐姆。 在源端串接一個33歐姆的電阻值,13+33=46大致相當于50,可以抑制從終端反射回來的信號再次反射。 (必須檢查傳輸線的特性阻抗......)。 在信號接收端接一個小電阻。 沒有公式理論:如果信號接收端的輸入阻抗很大,可以并聯一個51歐姆的電阻,并將內阻的另一端連接到參考地,以抑制信號端反射。 信號接收端串聯電阻。 從抑制信號反射的角度來看,只有端子輸入的電阻大于50歐姆。 但設計IC時,考慮到接收的能量,接收端的輸入內阻不會設計得小。 (這個反射怎么理解?能量反射,知道的同學可以回答)。 在信號線上串接內部電阻可能還有另一個目的:ESD。 例如,在USB插座上,在端的D+和D-上連接一個小電阻,例如10歐姆。 這是因為端的ESD無法通過。

答案B:通常高速數字信號傳輸線都有內部串聯的電阻來解決阻抗匹配問題。 阻抗不匹配會導致信號反射。 電磁波和光一樣,在同一介質中傳播,其能量不會衰減。 但如果光從一種介質發射到另一種介質時,會發生反射和折射,因此到達終端的光的能量會衰減很多。 同理,高速數字信號從源到終端的傳輸過程中,由于連接線或其他原因會造成一些阻抗不連續(例如要求傳輸線的阻抗為100歐姆,但有些PCB部分為100歐姆電阻的串聯和并聯教學視頻,中間鉆盲孔(或者線寬變化會導致阻抗不連續),會引起信號反射。 反射信號將與傳輸線上的原始信號疊加。 信號會受到干擾,終端接收到這樣的信號就會出現解碼錯誤。 USB 插座上的線電阻就是用于此目的。 一般來說,如果內阻為0歐姆,就沒有問題。 但如果USB僅傳輸低速信號,則沒有問題,阻抗要求也沒有那么嚴格。 而如果傳輸高速USB信號出現問題,串接一個小電阻值或許可以解決誤碼問題。 ESD元件通常采用一定的路徑或方法將靜電盡可能傳導到地或電源,以防止對芯片產生影響。 因此,ESD元件的一端必須接地,而不是串聯在電路中。