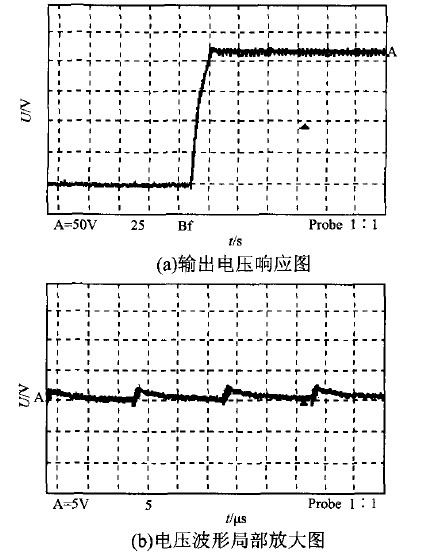

本文的目的:讓人了解下DCDC電路負載能力對開關頻度的影響變化。

本文所需的實驗條件:5V降3.3V的DCDC降糖電路,滑動變阻器RL,示波器,萬用表,5V直流電源。

測試描述:本文所涉及到的測試參數存在偏差,電流值偏差為±0.05V,內阻值偏差為±2Ω,偏差不是問題,但讓人就能理解的大致方向是對的。

首先來了解幾個詞匯:

(1)負載:指聯接在電路中的電源兩端的電子元件。

(2)負載率:指的是實際負荷量與額定負荷量的比值,通常用百分率標識。

(3)空載:電源電路帶載能力中的一種情況,指電路中的電源沒接任何元件。

(4)輕載:電源電路帶載能力中的一種情況,指在電路的負載范圍內,負載率在30%以下(這個沒有嚴格定義,有些覺得是15%,有些覺得是50%)。關于輕載就是負載阻值大,這個在有些情況下是不一定的,如在恒流源的負載中,內阻小負載才輕;在恒壓源的負載中電流過大怎么處理,阻值大時負載輕。(本文是以恒壓源為例)

(5)重載:電源電路帶載能力中的一種情況,指在電路的負載范圍內,負載率在80%以上有些覺得是85%)。

(6)滿載:電源電路帶載能力中的一種情況,指在電路的負載范圍內,負載率達到了100%。(可以覺得是負載為0歐時的情況)

(7)適載:本文新增,自定義在輕載和重載之間,可以覺得是負載療效最好的一種。

(8)上升沿和增長沿:認識下波形中的“上升沿”和“下降沿”是指的哪部份(如右圖)

本文是以右圖的DCDC降糖電路為例,可以看作是恒壓源。電路中以滑動變阻器為負載RL,用示波器檢測電路中LX處的開關頻度,當改變RL后再看LX處開關頻度波形的變化。

下邊開始實驗:

1、這是空載時LX處的檢測波形(即負載RL不接時):

該圖說明了當不接負載RL時也不是完全的空載,由于從電路中看還有R430、R431和C283、C284這種元件構成了電源本身的負載,所以會出現如圖波形。

2、這是接入負載RL且電阻為0歐時LX處的檢測波形:

測得電源輸出:3.3V/1.6A,P=UI=3.3*1.6=5.28W,此輸出可以看作滿載輸出。

圖中增長沿那邊已缺位好多了,說明負載很重,電流拉不上來。

3、這是接入負載RL且電阻為2歐時LX處的檢測波形:

測得電源輸出:3.3V/2Ω/1.4A,P=UI=3.3*1.4=4.62W,負載率為(4.62/滿載時輸出功率)*100%=87.5%,此輸出可以看作重載輸出。

隨著負載電阻的增加,這兒的增長沿也漸漸在倒塌。

4、這是接入負載RL且電阻為5歐時LX處的檢測波形:

隨著負載電阻的增加,圖中增長沿部份開始變化。

5、這是接入負載RL且電阻為6歐時LX處的檢測波形:

測得電源輸出:3.3V/6Ω/0.587A,P=UI=3.3*0.587=1.9371W,負載率為(1.9371/滿載時輸出功率)*100%=36.6875%,小于30%,此輸出可以看作適載輸出。

6、這是接入負載RL且電阻為47歐時LX處的檢測波形:

隨著負載電阻的降低,如圖中上升沿部份底端凹坑變寬,喻示了上升沿將開始坍塌。

7、這是接入負載RL且電阻為53歐時LX處的檢測波形:

隨著負載電阻的降低,如圖中上升沿部份漸漸倒塌。

8、這是接入負載RL且電阻為76歐時LX處的檢測波形:

隨著負載電阻的降低,如圖中上升沿部份坍塌越來越厲害。

9、這是接入負載RL且電阻為96歐時LX處的檢測波形:

測得電源輸出:3.3V/96Ω/0.034A,P=UI=3.3*0.034=0.1122W,負載率為(0.1122/滿載時輸出功率)*100%=2.125%,大于30%電流過大怎么處理,此輸出可以看作輕載輸出。

10、這是接入負載RL且電阻為100歐時LX處的檢測波形:

11、這是接入負載RL且電阻為300歐時LX處的檢測波形:

隨著負載電阻的降低,如圖中上升沿部份坍塌越來越厲害,說明負載輸出越來越輕。

12、這是接入負載RL且電阻為437歐時LX處的檢測波形:

此圖為動態時的照相圖

此圖為動態中抓取的單個圖

測得電源輸出:3.3V/437Ω/0.007A,P=UI=3.3*0.007=0.0231W,負載率為(0.0231/滿載時輸出功率)*100%=0.4375%,大于30%,此輸出可以看作輕載輸出,輕到一定程度波形跳動很大。

推論:

DCDC降糖電路中負載的變化影響到了開關頻度的變化,負載變輕時在開關頻度波形的上升沿那邊變化可以反映下來,當負載變重時在開關頻度波形的增長沿那邊變化可以反映下來。

,DCDC電路的開關頻度在EMC測試時須要注意到其幅射性。