日前,北方科技學院深港微電子大學李毅達助理院長課題組在下一代存算芯片領域取得重要進展,相關研究成果相繼發表在國際頂尖刊物、材料領域著名刊物、ACSOmega(獲選為封面文章)。

隨著對數據驅動型應用(比如新一代機器學習加速器和物聯網)需求的持續下降,傳統的馮?諾依曼構架面臨著嚴重的“存儲墻”挑戰,硅基晶體管工藝制程的縮小進一步激化了此類情況。為了突破該困局,集儲存單元和估算單元為一體的單片三維集成或則存內估算,成為一種潛在的解決方案。但用于CMOS前端集成的硅基技術深受高熱負載(<400℃)的限制,二維材料、氧化物半導體等這種超硅元件可以挺好地兼容CMOS前端工藝。盡管這么,這種新型電子材料并不成熟,在材料、器件機理和生長工藝還須要特別深入的研究以實現未來產業化的可能。李毅達課題組旨在于解決這種問題,在可CMOS后道集成的邏輯元件、新型儲存元件發表了一系列的工作如下:

:用于實現CMOS前端兼容儲存陣列和邏輯電路的高性能原子層沉積ZnO薄膜晶體管

氧化物半導體具有工藝氣溫低、透明度好、薄膜可大面積生長、電子遷移率高、能帶隙寬等優點量子通訊 優點,這種優點使其適用于顯存驅動電路以及基于高性能薄膜晶體管的邏輯電路。隨著人們對實現具有新功能和強悍估算能力的新型估算構架越來越感興趣,開發高性能氧化物半導體晶體管以實現兼容CMOS前端工藝的單片三維集成(M3D)電路已迫在眉睫。

在這項工作中,首先借助原子層沉積(ALD)工藝,實現了基于多晶ZnO半導體的高性能薄膜晶體管(TFT),該TFT的電子遷移率可達140cm2/V·s,電壓開關比>108,基極漏電壓

該項工作相關成果以“CMOS-of-LineArrayandLogicbyHighLayerZnOThin-film”為題發表在國際頂尖刊物上。該工作得到了深港微電子大學老師,以及其他合作單位(上海郵電學院、香港學院、上海交通學院)老師的支持。李毅達課題組2022級博士生王文輝為論文第一作者,李毅達為第一通信作者,張盼盼(上海郵電學院)和林龍揚為共同通信作者,北方科技學院深港微電子大學為論文第一通信單位。

圖1:可兼容CMOS前端集成的ZnO薄膜晶體管,及其儲存陣列和邏輯電路

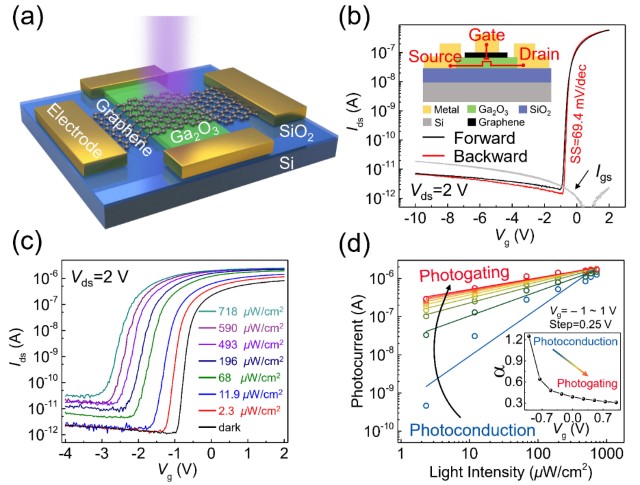

:基于的RRAM性能優化及其4K濕度下的阻變特點研究

近些年來,基于金屬氧化物的RRAM已在人工神經網路(ANN)中應用,并取得了巨大成功,但其性能指標還具有進一步優化的空間。在此基礎上量子通訊 優點,本項工作研究出了一種使用原子層沉積(ALD)制備摻鋅氧化鉿的阻變儲存器(HfZnORRAM)的合金化方式,并實現了元件性能的提高。與傳統氧化鉿(HfOx)RRAM相比,HfZnORRAM具有更低的工作電流(相比之下降低超過20%)和阻變煤耗(相比之下降低超過3倍),以及更均勻的電流和內阻分布。據悉,通過使用恒壓脈沖方案,HfZnORRAM可以實現多態可調制特點(即模擬突觸特點)且呈現出良好的可重復性。同時,本項工作也對HfZnORRAM在4K的超低濕度下進行了表征,驗證其高溫下功能特點的同時揭示了其自旋傳輸機制。本項工作展示了參雜RRAM在廣泛水溫范圍內尤其是在高溫下應用的潛力,包括將其應用于量子估算和深空探求。

該項工作相關成果以“of-BasedRRAManditsdownto4K”為題發表在上。該工作得到了深港微電子大學老師,以及其他合作單位(臺灣學院、上海交通學院、江波龍電子股份有限公司)老師的支持。李毅達課題組2023級博士生蘭峻為論文第一作者,李毅達為通信作者,北方科技學院深港微電子大學為論文第一通信單位。

圖2:基于的RRAM元件結構及其突觸特點和高溫阻變特點

ACSOmega(封面文章):采用液態金屬做電極的全氨水制備、無機、多態憶阻器

本項工作報導了一種基于釩酸鉍(BiVO4)和二硅氧烷(TiO2)的濾液法的憶阻元件,該元件以鎵基晶界鎵-銦(EGaIn)和鎵-銦-錫合金()液態金屬作為頂電極。通過材料表征發覺,BiVO4和TiO2產生了一種無孔結構,可以實現高效的阻值開關。據悉,鎵基液態金屬(GLM)接觸式憶阻器在?10至+90°C的寬氣溫范圍內均表現出穩定的憶阻行為且能在溫度下表現出優異的長程提高(LTP)和長程提高抑制(LTD)的突觸行為。借助元件的突觸特點在多層感知器(MLP)網路中進行模擬,可以實現約90%的手寫辨識確切率。這項研究結果為氨水制備發和基于GLM的憶阻元件鋪平了公路,該類憶阻器可用于惡劣環境下柔性基板上的神經形態相關的應用場景中。

該項工作相關成果以“All-,for”為題發表在ACSOmega上,并被主編選為當期封面文章。李毅達課題組博士后為論文第一作者,李毅達為通信作者,北方科技學院深港微電子大學為論文第一通信單位。

圖3:純堿液憶阻元件結構、阻變特點及其突觸特點圖4:刊物封面

論文鏈接:

1.Wang,W.,Li,K.,Lan,J.etal.CMOS-of-linearrayandlogicbyhighlayerZnOthin-film.Nat,6079(2023).

2.Lan,J.,Li,Z.,Chen,Z.,Zhu,Q.,Wang,W.,,M.,Lu,J.,Liang,J.,fú,M.,Chen,P.,Chen,K.,Zhang,G.,Wang,Z.,Zhou,F.,Lin,L.,Li,Y.,of-BasedRRAManditsdownto4K.Adv..Mater.2023,9,.

3.,Aziz-Ur-RahimBacha,IqraNabi,JunLan,Wang,Meifú,KaiChen,Zhang,Zhou,Lin,,,Awais,andYidaLi,ACS(45),40911-40919.DOI:10.1021/.